Aprenda como funcionam os flip-flops JK e onde são usados em circuitos digitais

2025-10-17

7468

Catálogo

Compreendendo o flip-flop JK

Um flip-flop JK é um circuito digital usado para armazenar um bit de dados.É um alicerce principal em contadores, unidades de memória e sistemas de controle.Como outros flip-flops, ele muda de estado com base em um relógio (CLK) sinal, que determina quando a saída é atualizada.O flip-flop JK melhora o mais simples Trava SR eliminando seu estado inválido.Ele usa duas entradas, J. e Ke uma entrada de relógio.Os sinais J e K controlam se a saída P é definido, redefinido, mantido ou alternado.O nome JK não descreve o que as entradas fazem; foi escolhido para distinguir este design dos anteriores.A maioria das fontes atribui o nome a Jack Kilby, que desenvolveu o conceito de circuito.

O flip-flop JK só muda sua saída quando o clock está ativo.Seu comportamento depende da combinação dos valores J e K:

|

CLK |

J. |

K |

Próximo

P |

Operação |

|

0 |

X |

X |

P |

Sem alteração |

|

1 |

0 |

0 |

P |

Esperar (memória) |

|

1 |

1 |

0 |

1 |

Definir |

|

1 |

0 |

1 |

0 |

Reiniciar |

|

1 |

1 |

1 |

Q̅ |

Alternar |

• Definir: Quando J = 1 e K = 0, a saída torna-se 1.

• Reset: Quando J = 0 e K = 1, a saída torna-se 0.

• Hold: Quando J = K = 0, a saída permanece a mesma.

• Alternar: Quando J = K = 1, a saída muda para o estado oposto.

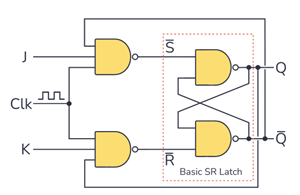

Figura 2. Flip-flop JK construído usando portas NAND e uma trava SR (Set-Reset)

A capacidade de alternância do flip-flop JK o torna especialmente útil para contagem binária e divisão de frequência.É construído a partir de portas lógicas, normalmente Portas NAND ou NOR, dispostos em torno de um básico Trava SR.As saídas realimentam as portas de entrada, permitindo que o circuito alterne quando J e K estão altos, o que torna o flip-flop JK mais flexível do que a trava SR.No entanto, em um flip-flop JK acionado por nível, se o clock permanecer alto enquanto J e K forem 1, a saída poderá alternar rapidamente entre 0 e 1 antes que o clock caia.Essa oscilação indesejada é conhecida como problema de corrida.

Compreendendo o símbolo do flip-flop JK

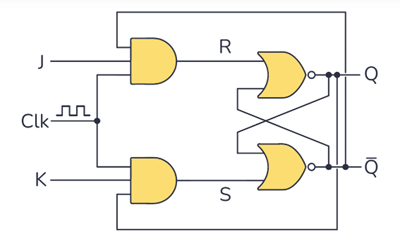

Figura 3. Símbolos do flip-flop JK

O flip-flop JK tem duas entradas principais, J e K, e duas saídas, Q e Q̅.Ele também inclui uma entrada de clock (CLK) com um indicador de borda que mostra se ele responde à borda ascendente ou descendente do sinal de clock.Algumas versões incluem opcional Predefinição (PRE/SET) e Limpar (CLR/R) entradas para controle assíncrono, permitindo que a saída seja configurada ou redefinida instantaneamente, independente do relógio.

Um triângulo na entrada do relógio (CLK) indica um flip-flop acionado por borda positiva, o que significa que ele é atualizado quando o sinal do relógio transita de 0 a 1.Um triângulo com uma bolha representa um flip-flop acionado por borda negativa, que é atualizado quando o sinal do relógio passa de 1 a 0.A bolha na entrada Preset (PRE) ou Clear (CLR) mostra que a entrada está ativo baixo.Para interpretar o símbolo corretamente, primeiro identifique o marcador da borda do clock, depois verifique as entradas PRE e CLR e, finalmente, relacione as entradas J e K com a tabela verdade para a operação correta.

Tipos de chinelos JK

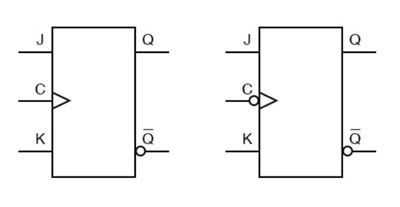

1. Flip-flop JK acionado por pulso (mestre-escravo)

Figura 4. Diagrama de circuito do flip-flop JK mestre-escravo

Um flip-flop JK acionado por pulso é um íon v ariat do flip-flop JK padrão que atualiza sua saída somente após um pulso de relógio completo.Ele usa a configuração mestre-escravo para eliminar o problema de corrida, garantindo transições de saída estáveis e previsíveis.

Um flip-flop JK acionado por pulso consiste em duas travas conectadas em série:

• O mestre trava captura valores de entrada (J e K) quando o relógio (CLK) é alto.

• O escravo trava atualiza a saída final (Q) quando o relógio fica baixo.

Essa sequência garante que ocorra apenas uma alteração de saída por pulso de clock completo, tornando o circuito mais estável e confiável.

Como funciona a configuração mestre-escravo?

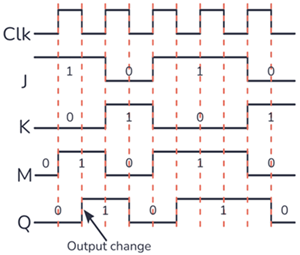

Figura 5. Diagrama de temporização de um acionado por pulso (mestre-escravo)

Aqui está o que acontece passo a passo:

• Borda ascendente (0 → 1): A trava mestre fica ativa.Ele lê as entradas J e K e atualiza seu estado interno de acordo.

• Clock High: Enquanto o clock permanece alto, a trava escrava permanece inativa, mantendo o estado de saída anterior.

• Falling Edge (1 → 0): A inversão do clock ativa o latch escravo, transferindo o estado armazenado do mestre para a saída Q.

A saída muda somente após um ciclo de clock completo (0 → 1 → 0).Esse comportamento controlado dá nome ao circuito: flip-flop JK acionado por pulso.

Tabela verdade de um flip-flop JK acionado por pulso

|

Relógio

Pulso |

J. |

K |

Próximo

P |

Operação |

|

0 ou 1 (sem pulso completo) |

X |

X |

P |

Sem alteração |

|

0 → 1 → 0 |

0 |

0 |

P |

Memória (Espera) |

|

0 → 1 → 0 |

1 |

0 |

1 |

Definir |

|

0 → 1 → 0 |

0 |

1 |

0 |

Reiniciar |

|

0 → 1 → 0 |

1 |

1 |

Q̅ |

Alternar |

Cada ação ocorre apenas uma vez por pulso de clock completo, evitando múltiplas alternâncias durante um único período de clock.

O flip-flop JK mestre-escravo oferece operação estável e confiável, evitando o problema de corrida - sua saída muda apenas uma vez por pulso de clock, mesmo quando ambas as entradas estão altas.Ao separar a captura de entrada e a atualização de saída, evita falhas e garante temporização precisa, tornando-o ideal para contadores e circuitos de controle.Para funcionar corretamente, as entradas (J e K) devem permanecer estáveis em torno da borda do clock, o pulso do clock deve ter a largura correta e o atraso de propagação através de ambas as travas deve ser gerenciado para manter a velocidade e a estabilidade.

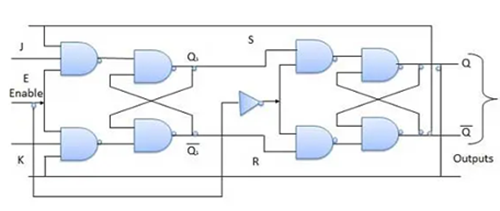

2. Como funcionam os flip-flops JK acionados por borda?

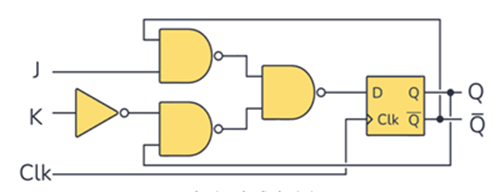

Figura 6. Flip-flop JK acionado por borda

Um flip-flop JK acionado por borda é um tipo de circuito digital que altera sua saída apenas em uma transição de clock específica, conhecida como borda.Ao contrário do flip-flop JK mestre-escravo, que requer um pulso de clock completo (0→1→0) para atualizar, a versão acionada por borda reage instantaneamente a uma única transição de clock, seja uma borda ascendente (↑) ou uma borda descendente (↓).Este projeto melhora a precisão do tempo e elimina o problema de corrida encontrado em circuitos acionados por nível.

Como funciona o disparo de borda?

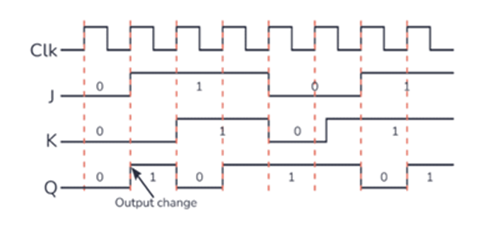

Figura 7. Operação de um flip-flop JK acionado por borda

Em um flip-flop JK acionado por borda, as entradas J e K são amostradas apenas no momento da transição do clock.Uma vez que essa borda ocorre, o flip-flop atualiza sua saída (Q) com base na combinação atual de entrada.Entre as arestas, a saída permanece estável e não é afetada por alterações em J ou K.

Os flip-flops acionados por borda ascendente respondem quando o clock vai de baixo para alto (0→1), enquanto os acionados por borda descendente respondem quando o clock vai de alto para baixo (1→0).

Essa temporização precisa garante desempenho confiável em circuitos síncronos, como contadores, registradores e divisores de frequência.

Tabela verdade do flip-flop JK acionado por borda

|

Relógio

Borda |

J. |

K |

Próximo

P |

Descrição |

|

Sem borda ascendente |

X |

X |

P |

Sem alteração |

|

↑ (0 → 1) |

0 |

0 |

P |

Esperar (memória) |

|

↑ (0 → 1) |

1 |

0 |

1 |

Definir |

|

↑ (0 → 1) |

0 |

1 |

0 |

Reiniciar |

|

↑ (0 → 1) |

1 |

1 |

Q̅ |

Alternar |

A saída muda apenas na transição do clock, garantindo que Q seja atualizado uma vez por transição.Este comportamento torna o flip-flop JK ideal para sistemas digitais sensíveis ao tempo.

Um flip-flop JK acionado por borda pode ser feito usando um flip-flop D de borda ascendente, junto com portas NAND e NOT.O sinal é aplicado ao flip-flop D para produzir um comportamento JK que é atualizado apenas na borda ascendente do clock.Essa configuração evita problemas de corrida, fornece saída estável e consistente, simplifica o controle de temporização e é amplamente utilizada em circuitos integrados e simulações digitais para desempenho confiável.

Circuitos integrados flip-flop JK

|

CI |

Sandálias de dedo

por ficha |

Acionar

Tipo |

Especial

Entradas |

Tecnologia |

Típico

Fornecer |

|

CD4027 |

2 |

Borda positiva |

Definir, redefinir |

CMOS |

3V–15V |

|

74HC73 |

2 |

Borda negativa |

Claro |

CMOS |

2V–6V |

|

74LS73 |

2 |

Borda negativa |

Claro |

TTL |

5V |

|

74HC112 |

2 |

Borda negativa |

Predefinido, Limpar |

CMOS |

2V–6V |

Combine a tensão de alimentação e a família lógica com o resto do seu circuito para garantir compatibilidade e operação estável.Decida se você precisa de um dispositivo acionado por borda ascendente ou descendente com base em como o sinal do relógio foi projetado.Considere se sua aplicação requer apenas uma entrada de reinicialização ou funções predefinidas e limpas para uma inicialização adequada.Finalmente, sempre verifique as especificações de tempo de configuração, tempo de espera e atraso de propagação para ter certeza de que o flip-flop pode lidar com a frequência de clock pretendida do seu circuito.

Usos dos chinelos JK

• Contadores e divisores de frequência: defina J = K = 1 para alternar e encadear estágios para contagem mod-N.

• Registradores de deslocamento e conversão de dados: movimento de bits serial para paralelo e paralelo para serial.

• Registradores e pequena memória: elementos simples de armazenamento de flags e dados de controle.

• Máquinas de estado e lógica de controle: comportamento previsível de configuração, reinicialização, retenção e alternância para sequenciadores.

Vantagens e desvantagens dos chinelos JK

Vantagens

Operação versátil em um dispositivo: definir, redefinir, segurar, alternar

Modo de alternância natural para divisão por 2 e contagem

Disponível com preset assíncrono e clear

Modelo educacional claro para lógica sequencial

Desvantagens

Mais lógica interna do que um flip-flop D, o que aumenta a área e o atraso

Versões sensíveis ao nível podem correr quando J = K = 1 e o clock estiver alto

Sensível ao tempo se a configuração, retenção ou largura de pulso forem violadas

Conclusão

O flip-flop JK é uma parte importante do design digital porque é flexível e confiável.Pode funcionar como memória, contador ou divisor de frequência em um circuito.Saber como cada tipo funciona e gerenciar o tempo corretamente ajuda a construir um sistema estável e eficiente.

SOBRE NóS

Satisfação do cliente sempre.Confiança mútua e interesses comuns.

SOBRE NóS

Satisfação do cliente sempre.Confiança mútua e interesses comuns.

teste de funcionamento.Os produtos mais econômicos e o melhor serviço é o nosso compromisso eterno.

Artigo quente

- LM358 GUIA AMPLIFENCIADOR OPERACIONAL DO DULO

- O CR2032 e o CR2016 são intercambiáveis?

- Compreendendo as diferenças ESP32 e ESP32-S3 Análise técnica e de desempenho

- Escolhendo a bateria certa: um guia para AG4, LR626, LR66, 177/376/377, SR626 e SR626SW equivalentes

- NPN vs. PNP: Qual é a diferença?

- Noções básicas do transistor BC547: pinagem, circuitos de aplicação, modelos alternativos/complementares

- Esp32 vs STM32: Qual microcontrolador é melhor para você?

- O que é um MOSFET e como funciona?

- Relé elétrico básico: operação de trabalho, tipos e usos

- Transistores PNP: estrutura, princípio de trabalho e aplicação

Noções básicas sobre bombas: princípios básicos, tipos, especificações e problemas comuns

Noções básicas sobre bombas: princípios básicos, tipos, especificações e problemas comuns

2025-10-17

O que é um fotodiodo: princípios de funcionamento, modos, vantagens e aplicações

O que é um fotodiodo: princípios de funcionamento, modos, vantagens e aplicações

2025-10-17

perguntas frequentes [FAQ]

1. Por que o flip-flop JK é chamado de flip-flop universal?

É chamado de universal porque pode desempenhar as funções de outros flip-flops como os tipos SR, D e T, alterando a lógica de entrada condições.

2. O que acontece quando as entradas J e K são 0?

Quando J e K são ambos 0, o flip-flop JK mantém sua saída anterior estado.Nenhuma mudança ocorre até que as entradas ou o sinal do relógio mudem.

3. Como converter um flip-flop JK em um flip-flop T?

Conectando as entradas J e K juntas e configurando-as para lógica 1, o flip-flop JK alterna sua saída a cada pulso de clock, funcionando como um flip-flop T.

4. Qual é o atraso de propagação em um flip-flop JK?

O atraso de propagação é o curto tempo que leva para a saída (Q) mudar após o relógio ou a entrada mudar.Limita a velocidade máxima de operação em circuitos digitais.

5. Os flip-flops JK podem ser usados em microcontroladores?

Não diretamente, mas suas funções são frequentemente incorporadas registros e temporizadores do microcontrolador.No design de hardware, JK externo flip-flops são usados em aplicações de temporização ou contagem baseadas em lógica.

6. Quais portas lógicas são usadas para construir um flip-flop JK?

Os flip-flops JK são normalmente construídos usando portas NAND ou NOR dispostas em torno de uma trava SR, com loops de feedback que permitem alternar quando ambos J e K são altos.

7. Como testar um flip-flop JK em um circuito de laboratório?

Aplique um sinal de clock conhecido e varie as entradas J e K.Observe o saída usando LEDs ou um osciloscópio para confirmar definir, redefinir, manter e alternar operações.

Número da peça quente

UHE1H121MPD

UHE1H121MPD 0805YG105ZAT2A

0805YG105ZAT2A C3225CH2J103K125AA

C3225CH2J103K125AA TMK212B7473KD-T

TMK212B7473KD-T GRM0335C1HR60BA01J

GRM0335C1HR60BA01J GCM1885C2A7R0DA16D

GCM1885C2A7R0DA16D TPSD337K010R0150

TPSD337K010R0150 MAX1110CAP+T

MAX1110CAP+T MAX3221EUE+T

MAX3221EUE+T VSC7425XJG-02

VSC7425XJG-02

- EP2S130F1508C5

- ADM6996LCX-AD-T-1

- ISL28276IAZ-T7

- CY7C1460KV25-167BZXI

- MCC122-02io8

- SN74HC259PWR

- TMS370C742AFNTG4

- T491B226M006AT7280

- MC34063AMELG

- LTC2450CDC-1#TRMPBF

- LTC2057HVIDD#TRPBF

- TPS5420D

- DRV5033AJQDBZT

- LMR33630CDDAR

- TLV2444AQPWRQ1

- ADP3415LRM-REEL

- AM79C031JC

- AP3041AM-G1

- AT25640NC

- CY7C1346F-133ACT

- GT28F160C3TA90

- ISL1535AIVEZ

- LP3986TLX-3333

- LTC3407AIMSE-2

- MKL26Z256VLH7

- RSM2221-001

- SAF-C505L-4EM

- UPG132GV

- XC9536-VQG44AMM-10C

- EUA4890MIRI

- OPL-06650-BG

- SC6500B2

- M29W800DB70ZE6

- MN7D029P5A

- MSM82C37B-5G3-2K

- S1X55283F00B200

- BCM3185KMLG

- SUR2X100-12

- G40H65DFB